electronics engineering is an engineering science that has a very pure concept because life begins with the concept of electronics as well as the invention of brilliant inventions beginning from rene descartes to newton and EINSTEIN; electronics science is a concept of thinking technique is very eternal until now because all the equipment on earth today using the concept of electronics engineering thus our daily life must be aided by the concepts and tools and materials made of components electronic components. Electronic engineering stands highest above the concept of other fields of engineering both civil engineering and machinery and engineering informatics; at home ; in the office ; at the factory ; in the car ; in communications equipment; and also day to day activities we must come into contact with the components of electronic components in the form of instrumentation and control equipment that we always use and use such as: clock, hand phone, TV, computer, refrigerator, air conditioner, car, airplane, ship, electrical installation of house and building and factories, traffic lights, GPS (global positioning system), oil and gas well detector techniques, LED lights, radio and monitoring room in buildings and factories, video tron, running text and so forth. that's why let's learn the technique of electronics because of the highest purity and technical concepts.

XXX . XXX 4%zero null 0 1 2 3 4 digitally

Introduction to Number Systems

Why so many Number Systems?

Ask most people what the most commonly used number system is, and they would probably reply (after a bit of thought), the decimal system. But actually many number systems, and counting systems are used, without the users thinking much about it. For example clocks and compasses use the ancient Babylonian number system based on 60 rather than the decimal system based on 10. Why? Because 60 is easier to divide into equal segments, it can be evenly divided by 1,2,3,4,5,6,10,12,15, 20 and 30. This is much better for applications such as time, or degrees of angle than a base of 10, which can only be divided into equal parts by 1, 2 and 5.

Many counting systems are ancient in origin and are still in use because they are useful for particular purposes.

Using the decimal system it is easy to count up to ten fingers, using just the fingers on two hands. In northern Britain farmers, for centuries, used an ancient Celtic counting system, based on 20 (also called a score), to count their animals, and its use still persisted even into the second half of the twentieth century.

The binary system, based on 2, is just another special number system, and is used by digital electronic devices because digital circuits work on an electrical ‘on or off’ two state system, a number system based on 2 is therefore much easier for electronic devices to use. However binary is not a natural choice for human counting or calculation.

This module explains how binary, and some other number systems used in electronics work, and how computers and calculators use different forms of binary to carry out calculations. The important thing about this module is to get you to think about how the number systems work .

Binary Coded Decimal (BCD)

Representing Decimal Numbers

When calculations are carried out electronically they will usually be in binary or twos complement notation, but the result will very probably need to be displayed in decimal form. A binary number with its bits representing values of 1, 2, 4, 8, 16 etc. presents problems. It would be better if a particular number of binary bits could represent the numbers 0 to 9, but this doesn’t happen in pure binary, a 3 bit binary number represents the values 0 to 7 and 4 bit represents 0 to 15. What is needed is a system where a group of binary digits can represent the decimal numbers 0-9, and the next group 10-90 etc.

To make this possible, binary codes are used that have ten values, but where each value is represented by the 1s and 0s of a binary code. These special ‘half way’ codes are called BINARY CODED DECIMAL or BCD. There are several different BCD codes, but they have a basic similarity. Each of the ten decimal digits 0 to 9 is represented by a group of 4 binary bits, but in codes the binary equivalents of the 10 decimal numbers do not necessarily need to be in a consecutive order. Any group of 4 bits can represent any decimal value, so long as the relationship for that particular code is known.

In fact any ten of the 16 available four bit combinations could be used to represent 10 decimal numbers, and this is where different BCD codes vary. There can be advantages in some specialist applications in using some particular variation of BCD. For example it may be useful to have a BCD code that can be used for calculations, which means having positive and negative values, similar to the twos complement system, but BCD codes are most often used for the display of decimal digits. The most commonly encountered version of BCD binary code is the BCD8421 code. In this version the numbers 0 to 9 are represented by their pure binary equivalents, 4 bits per decimal number, in consecutive order.

BCD Codes

The BCD8421 code is so called because each of the four bits is given a ‘weighting’ according to its column value in the binary system. The least significant bit (lsb) has the weight or value 1, the next bit, going left, the value 2. The next bit has the value 4, and the most significant bit (msb) the value 8, as shown in Table 1.6.1.

So the 8421BCD code for the decimal number 610 is 01108421. Check this from Table 1.6.1.

For numbers greater than 9 the system is extended by using a second block of 4 bits to represent tens and a third block to represent hundreds etc.

2410 in 8 bit binary would be 00011000 but in BCD8421 is 0010 0100.

99210 in 16 bit binary would be 00000011111000002 but in BCD8421 is 1001 1001 0010.

Therefore BCD acts as a half way stage between binary and true decimal representation, often preparing the result of a pure binary calculation for display on a decimal numerical display. Although BCD can be used in calculation, the values are not the same as pure binary and must be treated differently if correct results are to be obtained. The facility to make calculations in BCD is included in some microprocessors.

One of the main drawbacks of BCD is that, because sixteen values are available from four bits, but only ten are used, there are several redundant values whichever BCD system is used. This is wasteful in terms of circuitry, as the fourth bit (the 8s column) is under used.

Try some simple conversions between Decimal and BCD8421

32110 to BCD8421

6523110 to BCD8421

001101110110 BCD8421 to decimal.

0011001011000110 BCD8421 to decimal.

Fig. 1.6.1 Seven Segment Display

Display Decoder/Drivers

Depending on the type of display some further code conversion may also be needed. One popular type of decimal display is the 7 segment display used in LED and LCD numerical displays, where any decimal digit is made up of 7 segments arranged as a figure 8, with an extra LED or LCD dot that can be used as a decimal point, as shown in Fig 1.6.1. These displays therefore require 7 inputs, one to each of the LEDs a to g (the decimal point is usually driven separately). Therefore the 4 bit output in BCD must be converted to supply the correct 7 bit pattern of outputs to drive the display.

Fig. 1.6.2 Driving a 7 Segment Display

The four BCD bits are usually converted (decoded) to provide the correct logic for driving the 7 inputs of the display by integrated circuits such as the HEF4511B BCD to 7 segment decoder/driver from NXP Semiconductors and the 7466 BCD to 7 segment decoder.

Question

BCD to 7 segment decoders implement a logic truth table such as the one illustrated in Table 1.6.2. There are different types of display implemented by different types of decoder, notice in table 1.6.2 that some of the output digits* may be either 1 or 0 (depending on the IC used). Why would this be, and what effect would it have on the display?

Notice that the 4 bit input to the decoder illustrated in Table 1.6.2 can, in this case, be in either BCD8421 or in 4 bit binary as any binary number over 9 will result in a blank display.

Alternative BCD Codes

Although BCD8421 is the most commonly used version of BCD, a number of other codes exist using other values of weighting. Some of the more common variations are shown in Table 1.6.3. The weighting values in these codes are not randomly chosen, but each has particular merits for specific applications. Some codes are more useful for displaying decimal results with fractions, as with financial data. With others it is easier to assign positive and negative values to numbers. For example with Excess 3 code, 310 is added to the original BCD value and this makes the code ‘reflexive’, that is the top half of the code is a mirror image and the complement of the bottom half, 5211 code is also self-complementing in this way. Some values in these BCD codes can also have alternative 1 and 0 combinations using the same weighting and are designed to improve calculation or error detection in specific systems.

Gray Code

Fig. 1.6.3 Four Bit Gray Code Disk

Binary codes are not only used for data output. Another special binary code that is extensively used for reading positional information on mechanical devices such as rotating shafts is Gray Code. This is a 4 bit code that uses all 16 values, and as the values change through 0-1510 the code‘s binary values change only 1 bit at a time, (see Table 1.6.4). The binary values are encoded onto a rotating disk (Fig. 1.6.3) and as it rotates the light and dark areas are read by optical sensors.

As only one sensor sees a change at any one time, this reduces errors that may be created as the sensors pass from light to dark (0 to 1) or back again. The problem with this kind of sensing is that if two or more sensors are allowed to change simultaneously, it cannot be guaranteed that the data from the sensors would change at exactly the same time. If this happened there would be a brief time when a wrong binary code may be generated, suggesting that the disk is in a different position to its actual position. The one bit at a time feature of gray code effectively eliminates such errors. Notice also that the sequence of binary values also rotates continually, with the code for 15 changing back to 0 with only 1 bit changing. With a 4 bit coded disk as illustrated in Fig. 1.6.3, the position is read every 22.5° but with more bits, greater accuracy can be achieved.

Introduction Logic Families

the differences and similarities between the various families of logic ICs available are described, along with their important operating conditions.

Logic 1 and Logic 0 are a bit more complex that 5V and 0V because these digital ICs are really little analogue circuits posing as ‘Digital’. A sort of sheep in wolves clothing!

Find out how logic gates actually work, and learn about the parameters that govern how the chips should be used. Special versions of the basic logic gates are also explained, such as Schmitt gates, open collectors, and buffers.

The 74 series of logic ICs introduced in this module, has been the backbone of digital electronics for about the last 50 years. Although nowadays they have been replaced in many applications by bigger, faster smarter chips, the 74 series families continue to play an important role in electronics, and learning about them is a sound basis for understanding the vital basics of digital electronics.

Logic Families Compared

Power, Speed and Compatibility

The logic gates are available in different combinations within I/C packages. As well as the basic logic functions, compatible ICs are available, which contain particular useful combinations of gates providing a convenient way of constructing more complex circuits. Hundreds of different, but directly inter-connectable logic ICs are available. The most commonly available logic ICs are the 74 series family and its sub−families, identifiable because their type numbers all start with the number 74.

the number 74.

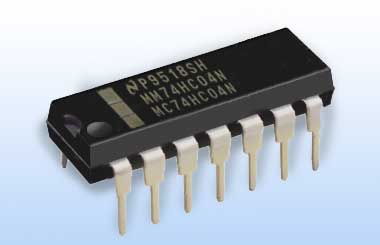

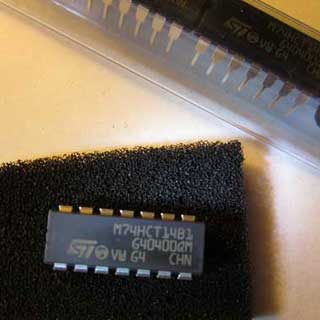

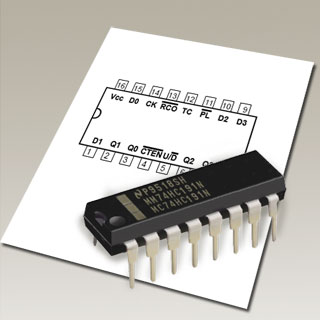

Fig.3.1.1 Logic IC Device Numbering

74 Series Device Identification

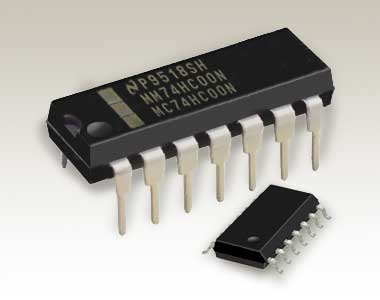

A typical 74 series IC is shown in Fig 3.1.1 and can be identified by the number MC74HC04N, which is a common structure for 74 series logic ICs, which breaks down into several sections as follows:

MC − One to three letter manufacturer’s ID code. (e.g. National Semiconductor/Texas Instruments)

74 − Commercial grade, IC plastic package with temperature range of 0°C to +70°C although some sub families have an extended range of − 40°C to +125°C.

(Also 54 Military/Aerospace grade, IC ceramic package with temperature range of −55°C to +125°C).

HC − Two to three letter code indicating sub-family (HC = High speed CMOS, HCT = High speed CMOS, TTL compatible).

04 − Two to four digit type number, indicates the type of circuit or gates with IC. 04 = Hex (6 per IC) Inverters.

N − One or two letter code for package type, e.g. N = DIP - Dual Inline Package. The codes used vary between manufacturers, but package details are usually included on the IC datasheet.

Compatibility between Logic ICs

The use of a single family within a circuit design with direct connections between ICs enables circuit designers to produce circuits consisting mainly of ICs, with few extra coupling or biasing components. This greatly reduces the component count of a circuit, which among other benefits, reduces size and increases reliability.

ICs of a particular family generally use a common technology, but ICs in other families, using different technologies, usually have different input and output requirements, different supply voltages, and other parameters that affect the use of digital ICs. Making direct connections between ICs of a single family or sub family is usually very simple. ICs of different families can sometimes also be directly connected together, but may require some extra circuitry at the interface of the two IC families to maintain compatibility.

Why these different families exist dates back to the 1960s when groups of logic ICs using different technologies first became available.

Scale of Integration

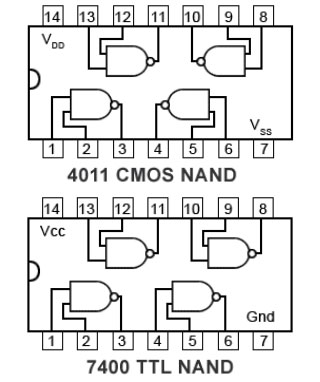

Fig. 3.1.2 Original CMOS and TTL Pinouts for Comparable NAND gate ICs

RTL (resistor-transistor logic) and DTL (diode-transistor logic), successfully used in early computers were superseded by TTL (transistor-transistor logic), which became the dominant technology. However as these ICs developed, at first as SSI (small scale integrated) devices, with just a few transistors per chip, and then as MSI (medium scale integrated) devices with 100 or more transistors, a problem arose that as more gates (and therefore more transistors) were packed into a single IC, the scale of integration would be limited by the power dissipation of the device.

Although each gate only dissipates a few milliWatts, the heat generated within a single large-scale integrated (LSI) circuit containing tens of thousands of transistors could potentially quickly destroy the IC.

It was therefore necessary to develop gates with much lower power consumption, so in the 1970s a series of CMOS (Complimentary Metal Oxide Semiconductor) ICs, called the 4000 series was developed, in which the power consumed by each gate was about 1/1000th of the power consumed by a similar TTL gate, making very large scale integration (VLSI) with millions, and more recently billions of transistors per chip possible. CMOS chips were also more flexible in their supply voltage requirements, working from supplies between 3V to 18V, compared with the TTL requirement for supplies of 5V +/- 0.25V. This made CMOS devices ideal for battery operation. However the speed at which these early CMOS devices operated was about 10 times slower than TTL.

These two logic families were not readily compatible; apart from the differences in supply voltage and speed, they were not particularly pin compatible, as illustrated in Fig. 3.1.2 so TTL chips, even simple ICs with the same types of gates as CMOS, could not be directly interchanged.

Power vs. Speed

Ideally logic gates should be able to change state immediately and consume little or no power. However the laws of physics, as presently understood, say that this is not possible. All electrical circuits must consume some power, and any change in the voltages and currents in that circuit must take at least some time.

Chip designers therefore had to try and reconcile the fact that higher speeds meant more power consumption, and so some families developed, using optimum speed whilst others were developed to use the minimum of power.

CMOS (Complimentary Metal Oxide Semiconductor) chips, designed for minimum power, got faster and TTL families, using bipolar transistors for optimum speed, were developed that not only increased speed but also reduced power consumption.

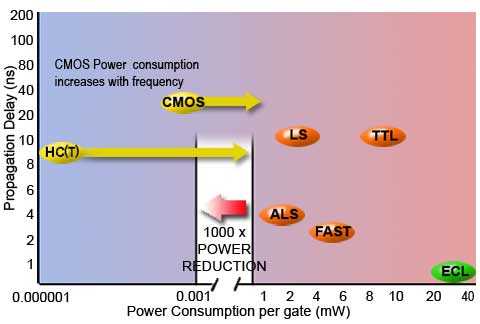

Fig 3.1.3 Logic Families Power vs Speed

As the overall performance of these families increased they also became more compatible. The increase in portable (battery powered) electronic devices along with the ability of chip manufacturers to make the component parts of ICs much smaller also meant that power could be reduced and speed increased.

Some of the main TTL and CMOS sub-families currently in use are compared in Fig. 3.1.3. Note how CMOS speed has been increased and power reduced with the introduction of the 74HC (High-speed CMOS) although (as the laws of physics demand), power consumption still increases, as the frequency at which they operate increases.

Because CMOS and TTL families can now operate at similar speeds and similar power consumption, the 74HCT (a CMOS sub-family compatible with TTL pinouts and voltage levels) now makes it possible to easily interface both families within in a single design, so enabling the use of the best features of each family.

74HC (and 74HCT for interfacing with the larger 74TTL families) are now recommended for most new designs.

The ECL Families

The ECL (Emitter Coupled Logic) families, originated in the late 1950s and remain the fastest chips available, but consume more power, and because they use a negative power supply (of −5.2V) have been difficult to interface with other families. This has changed with the introduction of PECL (Positive ECL) using a +5V supply, and LVPECL (Low Voltage Positive ECL) using a +3.3V supply. This now offers the opportunity of using mixed CMOS and TTL families at various power levels for logic operations and interfacing with ECL for high frequency digital communications.

How Logic Gates Work

Fig 3.2.1 Typical Logic IC Packages

Logic Technologies

Small and medium scale (SSI and MSI) Logic IC families are currently made in a wide range of sub-families and a variety of package types, using three basically different technologies:

• TTL (Transistor Transistor Logic)

• CMOS (Complimentary Metal Oxide Semiconductor)

• ECL (Emitter Coupled Logic)

Transistor Transistor Logic (TTL)

TTL gates use a 5V(±0.25V) supply, and are capable of high-speed operation. Over 600 different logic ICs are available, covering a very wide range of digital functions. Due to the use of bipolar transistors, TTL has much higher power consumption than similar CMOS types, when working at relatively low frequencies. As the frequency of signals handled increases however, this difference decreases as the power consumption of CMOS increases and TTL power consumption remains nearly constant.

TTL NAND Gate Operation

Fig. 3.2.2 Schematic diagram of a TTL NAND Gate

Notice that this circuit looks similar to those found in analogue push pull amplifiers, except that the transistors here are driven either into cut-off or saturation, rather than working in their linear operating condition. Also, being constucted within an IC, it can use a device not normally found in conventional analogue amplifiers, a multi emitter transistor.

Fig. 3.2.2 shows a typical schematic for a TTL NAND gate. R1 is a low value resistor (about 4K) and as the base current of T1 is small, the base voltage is about +5V. If both emitters of T1 are at logic 1, (also around +5V), there will be very little potential difference between base and emitter, and T1 will be turned off. As T1 is not conducting, its collector will also be at about 5V, and due to this high potential, T2 base will have a higher potential than its emitter, which will cause T2 to conduct heavily and go into saturation.

T2 collector will therefore fall to a low potential, and the emitter voltage of T2 will rise due to the current flow through R3. The voltage across R3 will rise to a sufficient level (about 0.7V) to fully turn on T3. As T3 saturates, its collector voltage will fall to about 0.2V, thus giving a logic 0 state at the output terminal.

T4 emitter voltage is made up of T3 VCE (about 0.2V) plus the forward voltage drop across D1, which will be about 0.7V, giving an emitter potential of 0.2V + 0.7V = 0.9V, the same as its base voltage.

The base potential of T4 is made up of T3 base/emitter potential VBE (about 0.7V), plus the collector/emitter, potential (VCE) of T2, (about 0.2V), giving a base voltage for T4 of about 0.9V. Therefore the base and emitter voltages on T4 are approximately equal, so T4 will be turned off.

With BOTH input terminals are at logic 1 therefore, the output terminal will be at logic 0, the correct operation for a NAND gate.

If either one of the inputs is taken to logic 0 however, this will make T1 conduct, as the emitter that is at logic 0 will be at a lower voltage than that supplied to the base by R1. This will cause T1 to saturate, taking its collector to a low potential (less than 0.8V) and as this is also connected to T2 base T2 will turn off, making its collector voltage and T4 base voltage, rise to very nearly +Vcc.

As virtually no current (ICE) is flowing through T2 collector/emitter circuit, practically no voltage is developed across the emitter resistor R3, reducing T3 base voltage to 0V, and so T3 is turned off. However, sufficient current will be flowing out of the output terminal (feeding the next gate input circuit) to cause T4 emitter to be held at about 4.1V. This is 0.9V below +Vcc, made up of the voltage across D1 (0.7V) plus the saturation voltage VCE of T4 (0.2V). This places about 4V or logic 1 (between 2.4V and 5V) on the output terminal.

Fig. 3.2.3 CMOS NAND Gate

Complimentary Metal Oxide Semiconductor (CMOS)

CMOS ICs can operate from a wide range of supply voltages (typically 3 to 18V, and lower with some sub families), with very low power consumption. The name CMOS (COMPLIMENTARY Metal Oxide Semiconductor) is used because opposite types, both P type and N type MOSFETs are used in the construction of these gates. Fig 3.2.3 shows a theoretical schematic circuit for a NAND gate.

CMOS NAND Gate Operation

T1 and T2 are P channel MOSFETs and either of these transistors will be turned on when logic 0 is applied to its gate. T3 and T4 are N channel MOSFETs and either of these transistors will be turned on by applying a logic 1 to its gate.

T1 and T2 are connected in parallel from supply to the output X, so switching either of them on will result in a logic 1 at output X.

T3 and T4 are connected in series between X and ground so when both are switched on, a logic 0 will appear at output X. The eventual logic state at X depends of course on the on or off state of the combination of all four transistors, and these are controlled by the logic states applied to the inputs A and B as can be seen in Table 3.2.1.

Input A controls T2 and T3 so that when logic 0 is applied, T2 is on and T3 is off. Logic 1 on input A reverses this condition.

Input B controls T1 and T4 so that logic 0 applied to B turns T1 on and T4 off. Logic 1 on input B reverses the condition.

Anti-Static Protection

Because MOSFETs, have a gate that is insulated from the transistor’s conducting channel, they can also be called Insulated Gate Field Effect Transistors (IGFETs) and have practically no current flowing into their inputs, therefore any high voltages due to static electricity are not reduced by current flow so can easily destroy the very thin insulating layer between the gate and the conducting channel of the transistor. To minimise such damage and protect the gates from any high voltage static electricity spikes that may appear across the IC during handling, CMOS ICs should always be stored in anti static packaging, and handled in accordance with manufacturers handling procedures.

Fig. 3.2.4 Anti Static Packaging

To protect the ICs from high voltage spikes when in circuit, protection diodes (see Fig. 3.2.3) are used at the gate inputs. Protection diode D3 is connected between input A and +Vcc so that if any voltage higher than Vcc appears at input A, D3 will become forward biased and conduct, limiting the input voltage to +Vcc.

Similarly, if a negative voltage appears at input A, D4 will conduct, limiting the input voltage to no less than 0V.

Input B is protected in a similar manner by D1 and D2. Note however, that although the diodes offer protection, it is still possible that very large static voltages may still damage these devices, so anti-static precautions should always be used when handling CMOS devices.

Capacitance in CMOS devices

Because CMOS transistors are IGFETs with insulating layers between electrodes, they naturally act as capacitors. The value of these capacitors is of course small because the electrodes either side of the insulating layer are extremely small. However the combined capacitance between the various sections of the several IGFETs that make up a CMOS gate, added to any capacitance between lead-out wires etc. is sufficient to have an effect on the overall gate performance. When a change in logic state occurs, ideally it should complete its transition from 0 to 1, or 1 to 0 immediately. However because of the gate capacitance and internal resistances that are present, the change cannot happen in less time than the CR time constant of the circuit. The output of a gate cannot complete its change until the input has completed its transition, and the output must similarly take some additional time, before reaching its new value.

Fig. 3.2.5 Propagation Delay

Propagation Delay

Any gate introduces some delay between when its input changes and when a resulting change takes place at its output. This is called the propagation delay of the gate, and is made up of two, often different delays, as shown in Fig. 3.2.5 using a simple inverter gate as an example.

The High to Low Propagation Time (tPHL) is measured from the time (usually in nanoseconds) when the input rises past the 50% level, to the time when the output falls past the 50% level. A similar, but usually longer delay (tPLH) is measured from when the input falls past the 50% level, to when the output rises past the 50% level. Therefore the average propagation delay of the gate is:

(tPHL + tPLH) / 2

Typical average propagation delay for a 74HC04 inverter is about 8ns.

Emitter Coupled Logic (ECL)

Fig. 3.2.6 ECL OR/NOR Gate

Because the early designs of ECL ICs needed a negative supply voltage of -5.2V they were not particularly compatible with either CMOS or TTL circuits, even though, like TTL, they use bipolar transistors. However there are now newer ECL sub families available that use positive supplies such as PECL (+5V) and LVPECL (+3.3V). Although the supply voltages for these ECL gates are now more compatible with CMOS and TTL, the logic levels used in ECL are quite different to other logic families. ECL is extremely fast in operation with propagation delays of less than 1 nanosecond available.

ECL was extensively used in early super computers, but because of its high power requirement (up to 40mW per gate) fell out of general use. Today modern ECL sub families such as PECL or LVPECL are now mainly used for interfacing CMOS or TTL digital systems to high frequency signal communication (up to several GHz) circuits. The two opposite logic state outputs (VOUTand VOUT) means that the ECL OR gate illustrated in Fig. 3.2.6 can operate as an OR gate or a NOR gate and also makes ECL ideal for interfacing with differential (two conductor) transmission lines possible. This method of transferring high speed digital data uses a pair of high frequency anti-phase signals as a method of cancelling out electromagnetic interference that may be picked up during transmission.

Operation

The basis of the ECL circuit is a differential amplifier (T3 and T4 in Fig. 3.2.6), which is ideal for high frequency use and reducing noise on the amplified signals. This amplifier compares the voltage at the inputs (the bases of T1 and T3) with a steady reference voltage produced by T5, D1 and D2. To avoid any delay caused by the transistors saturating, the differential amplifier is designed to always be in a linear amplifying mode, approximately half way between saturation and cut off.

The voltage change between logic 1 and logic 0 is between −0.9 and −1.75 respectively. Power consumption is considerably higher than CMOS or TTL because the transistors in the differential amplifier are always conducting, rather than switching on and off as in TTL and CMOS.

ECL and PECL use differential transmission, a pair of conductors with opposite polarity signals, along which data can be transmitted for around 50m. The technique reduces interference in the transmission lines when passing data from one digital system to another, and was used in many data transmission links in computing up to the 1990s, but for many uses, such as USB, HDMI etc. ECL has now been largely superseded by LVDS (Low Voltage Differential Signalling), a CMOS based high frequency digital transmission system. This system uses much less power than ECL and can transfer data over distances of up to 10m at a rate of several hundred Megabits per second.

Logic IC Parameters

Logic 1 and Logic 0 are not simply 5V and 0V or even Vcc and Ground. Within any family of ICs the voltages and currents indicating 1 and 0 cover defined ranges unique to that logic family. The range of voltages allowed for a particular logic level depends on the amount of current flowing into or out of the logic gate inputs or output, the larger the current the output is supplying, the lower the output voltage will be.

Each output will supply a certain amount of current before the output voltage falls too far to be called logic 1, and each gate input will need to be supplied with a certain amount of current to raise the input voltage sufficiently to be recognised as logic 1.

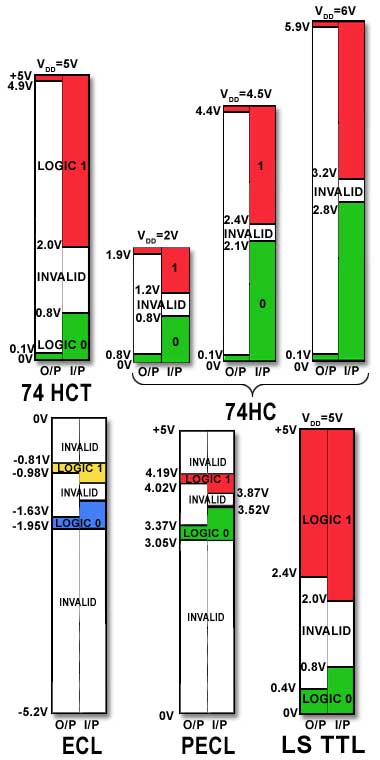

Examples of typical logic levels at inputs and outputs in a range of logic families are illustrated in Fig. 3.3.1. These levels are fairly standard throughout a particular family, although there can be minor differences in these and other parameters, between products from different manufacturers. In addition there are sub families within these families that may have different defined levels. When designing digital circuits, or replacing ICs in critical equipment, it is therefore essential to consult the appropriate manufacturer’s data sheets.

Logic 1 levels for inputs and outputs are shown in red and logic 0 in green. To highlight the fact that true ECL gates, have negative logic levels, these colours have been changed to yellow and blue respectively.

Notice that the logic levels for outputs (left column) and inputs (right column) in all of the families are different. This ensures that provided that the output voltage of a gate is within its defined logic limits for 1 or 0, any compatible gate input connected to that output will recognise the correct 1 or 0 levels. The difference between levels at the output and input in any particular family is called the ‘Noise Margin’.

Fig. 3.3.2 Logic IC Decoupling

Noise Margin

Because voltages in digital circuits can be continually changing very rapidly between logic 1 and logic 0, (virtually between supply voltage and ground), they have the potential to produce a lot of noise, in the form of high frequency voltage spikes on the IC power supply lines.

To counteract this it is important to include effective decoupling, not only at the power supply unit, but also by connecting decoupling capacitors across the VDD and 0V connections at each IC. These capacitors are normally connected as physically close to the IC as possible, as shown in Fig. 3.3.2.

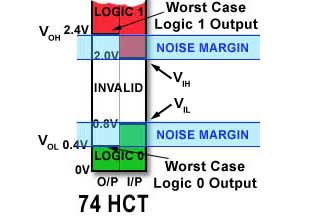

Fig. 3.3.3 Noise Margin

Despite these measures, it is possible that some noise will remain that could disturb the logic levels of digital signals. However logic ICs have a built in ‘Noise Margin’, illustrated in Fig. 3.3.3, This is the difference between the worst-case voltage ( VOH) for logic 1 at the output , which is 2.4V in the case of 74HCT, and the minimum voltage required for logic 1 to be recognised at the input (VIH), 2.0V in 74HCT. This difference (0.4V) should be enough to ensure that noise does not cause a wrong logic level to be seen by the 74HCT input; a similar noise margin is provided for logic 0 (VIL−VOL) as shown in Fig. 3.3.3.

It can be seen from Fig. 3.3.1 that different logic families have very different noise margins. The CMOS 74HC gates have a much wider noise margin than LS TTL or the TTL compatible 74HCT series, making them much more tolerant of noise. This is because the CMOS outputs are normally driven very close to VDD or 0V as very little current is drawn from a CMOS output to drive any CMOS inputs connected to it.

Minimising Power Consumption

In both CMOS and TTL ranges it is important that the central (white) range of voltages in Fig. 3.3.1 is avoided as much as possible. This is done by ensuring that switching between 1 and 0 is as fast as possible. If the IC is operating within the ‘invalid range’, power consumption increases dramatically. When the output voltage is close to the supply voltage, current is almost zero and therefore power (V x I) is very low. Similarly when the output is close to 0V but maximum current is flowing, V x I is again very low. Power consumption is at its highest when both voltage and current are around the mid range, and operating the ICs in this range would substantially increase the heat dissipated by the IC.

However, any unused inputs on CMOS ICs will tend to float to a mid voltage level, causing power dissipation to increase. To avoid problems with floating CMOS inputs, they should therefore be connected to either supply or ground, either directly or via a resistor, so they are not allowed to ‘float’ and cause excessive power consumption. This is not absolutely necessary, (though good practice), with TTL ICs as any unused TTL inputs will float up to logic 1.

Notice that ECL/PECL gates operate exclusively in this mid range area; this is why power consumption in these families is higher than in TTL or CMOS. However the close proximity of the logic 1 and logic 0 values in ECL allows for much higher switching speeds. This operation also gives ECL a much narrower noise margin however, making these chips more susceptible to noise. This is the reason for ECL having its positive supply tied to 0V, which is generally less noisy than sharing a positive supply with many other ICs.

Mixing Logic Families

The differences in the output voltage and/or current levels for TTL and the CMOS gates can affect circuit operation if both bipolar and CMOS logic families are used in the same circuit (e.g. LS TTL and HCT or CMOS), or if an older TTL IC is replaced by an ‘equivalent’ HCT chip during repairs or upgrading.

When mixing logic families it is important to consult input and output specifications such as those listed in Table 3.3.1 to ensure that the input and output conditions are compatible. The data in Table 3.3.1 shows typical input and output values for logic families, but particular ICs within a family or sub-family, and ICs from different suppliers will differ. The only way to be sure of complete compatibility is to consult the manufacturers data sheets for the ICs concerned.

Generally TTL outputs will interface to other TTL family inputs, and to 74HCT, which has TTL level inputs and CMOS level outputs.

The 74HCT outputs will interface to CMOS inputs provided both ICs are working from a common +VDD supply. This should not be a problem with the 74HC series, as it will operate on 5V supplies.

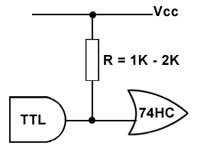

Fig. 3.3.4 Interfacing TTL to 74HC

Connecting a TTL output to a CMOS HC input may work if TTL input is not heavily loaded. A problem occurs however when more current is sourced by the TTL logic 1 output. Its output voltage (VOH) depends on the current being drawn from it and will vary from around 3.3V with no load current, down to about 2.4V when the output is sourcing around 400µA. As the HC gate input requires a minimum input voltage (VIH) of 3.2V there is a chance that at some output current between 0 and 400µA the TTL output will fall below 3.2V, and fail to be recognised as logic 1 by an HC input using its maximum supply voltage of 16V. Even if the HC supply is reduced to 4.5V there will still be a chance of mismatch.

The remedy is to fit a pull up resistor from the TTL output to Vcc as shown in Fig 3.3.4, which will increase the TTL output voltage (VOH) sufficiently to ensure correct interfacing. The value of the resistor should be between 1K and 2K ohms, the optimum value depending on the Fan out factor of the TTL gate and the number of gates being driven, the less current the output is sourcing, the lower the value of pull-up resistor needed.

Level Translation

With the older +5V TTL and +3V to +18V 4000 CMOS families the logic levels must be shifted considerably. For this purpose, a level translator IC such as the MC14504B from ON Semiconductor will provide level shifting for up to six ICs with VCC or VDD at any value between +0.5V and +18V. An alternative solution to level translation is to use Open Collector ICs.

ECL to TTL interfacing is carried out by ICs such as the MC10ELT25 from ON Semiconductor.

Sinking and Sourcing

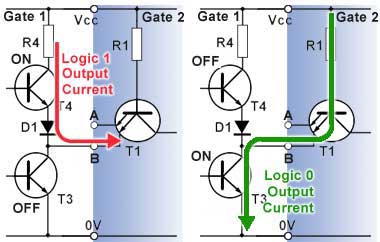

Fig.3.3.5 Sinking and Sourcing

Because the output circuits of logic gates are a type of push-pull or ‘Totem Pole’ output with only one of its two output transistors conducting at any one time, when the output terminal is at logic 1 T4 is turned on the output terminal of Gate 1 will supply (or SOURCE) current via T4 and D1 to the input of Gate 2. This will cause gate 2 input to also be at its logic 1 state as shown in Fig. 3.3.5 (a).

When gate 1 output is at logic 0, T4 is turned off and T3 is turned on, and output current will now flow in the opposite direction, from the input of Gate 2 in Fig 3.3.5 (b) and via T3 collector and emitter to ground; this is called SINKING the current.

When a LS TTL gate output acts as a source, a maximum source current of -400µA is available to be drawn from the output terminal. Note that the minus sign used in this case signifies a current that is flowing FROM the gate output. When the output is sinking current, the LS TTL gate is able to sink 8mA. Notice the sink current has no minus sign as it flows into the output terminal.

Fan Out

A standard LS TTL gate is therefore able to sink 20 times the amount of current it is able to source. This ratio between sinking and sourcing current is typical with bipolar gates. The above conditions mean that the output of a standard LS TTL gate is capable of driving up to 20 LS TTL inputs without its output voltage falling below the minimum specified for logic 1. This is described as a FAN OUT FACTOR of 20, but each logic family has its own particular ratio of sinking to sourcing currents, so the fan out factor of 20 is only correct where a standard LS TTL gate is driving one or more gates of the same (LS TTL) family.

Because gates of other families have different input and output currents the actual fan out factor will be different when logic families are mixed within a circuit. For example, Table 3.3.2 shows how mixing LS TTL and CMOS HC gates affects their fan out factors.

A 74HC output can feed up to 4000 74HC inputs, because the input currents of 74HC gates are extremely low, but only 10 74LS TTL inputs.

A Standard LS TTL gate output can drive up to 20 LS TTL inputs, but one LS TTL gate output can drive a virtually infinite number of 74HC CMOS gates because of the low current requirement of 74HC CMOS gates.

High Frequency AC Fan Out **

However, although a standard LS TTL output will apparently feed an infinite number of 74HC inputs (** in Table 3.3.2), when high frequency signals are used, additional limits need to be considered. Each CMOS input and output has a capacitance of several pF, and if a CMOS output is to feed a number of inputs, the individual input capacitances are in effect connected in parallel (and so add) to form a larger capacitance across any output driving the CMOS inputs.

The effect of this capacitance, as well as any capacitance due to connecting lines on the printed circuit board will combine with the output impedance of the gate to form a low pass filter. The effect of this filter will be to remove some of the higher frequencies in the signal, increasing rise and fall times, lengthening propagation delay and potentially causing timing errors in the system, therefore large fan outs are best avoided. These effects make the design of high-speed digital systems similar in some respects to high frequency RF circuits where stray capacitance, cable routing and interference play a large part in the circuit design.

Special Purpose Logic ICs

Open Collector Gates

Fig. 3.4.1 shows the internal circuit of an open collector NAND gate. The grey area illustrates a single gate within an IC. Instead of the normal Totem Pole output stage, the single output transistor T3 has its collector brought out to an external pin, which can be connected to an external power supply, at a different voltage to the VCC supply of the IC, via an external load resistor REXT.

In Fig. 3.4.1, when both inputs A and B are at logic 0, the high voltage applied to T1 base will cause it to turn on, so that T1 collector will go to near 0V and T2 will turn off.

As T2 is off there will be virtually no current through R3 so the voltage at T3 gate will be around 0V. T3 will therefore be turned off and the external pull up resistor REXT will pull the collector voltage of T3 up to +V, which will be at the valid logic 1 level of the next gate.

Logic Level Translation

Open collector and open drain gates can therefore be used for changing the levels of an output to match the higher or lower logic levels of an input on a different family of gates, when gates of mixed families are used.

Open collector gates can be used with external collector VCC supplies having a voltage typically somewhere between +1.5V to +5.5V for logic gates, Buffer ICs are also available that can operate on collector VCC supplies up to +30V. The maximum value of collector voltage is set by the VOH parameter of the open collector gate.

Fig 3.4.2 Wired AND Function

Wired Logic Functions

Open collector ICs are available in most of the logic types, AND, NAND etc, with the exception of OR gates. However open collector gates can be used to make both wired AND and wired OR functions as shown in Figs. 3.4.2 and 3.4.3. The outputs of gates without open collectors must not be connected together, because if the outputs happen to be at opposite logic states, the gate with a logic 0 output will try to sink more current than the logic 1 gate can source, and damage will most probably occur. However with open collector (or drain) gates, a gate output at logic 0 will be sinking current drawn from the external pull up resistor REXT, and any other connected open collector gate trying to output a logic 1 will have its output transistor turned off and so will not be sourcing any current.

Wired AND

If two or more open collector gate outputs are connected together, any gate with a logic 0 output will pull all other connected outputs to logic 0, giving an output of logic 0 at output X, but if all the connected outputs are at logic 1, then X will be at logic 1, the action of an ‘invisible’ AND gate.

Fig 3.4.3 Wired OR Function

Wired OR

It is also possible to implement a wired OR function using open collector (or drain) gates as shown in Fig. 3.4.3, although the explanation here is a little more complex as it involves using Negative Logic.

The circuit in Fig. 3.4.3 is used to obtain the Boolean function (A•B)+(C•D) without using a physical OR gate.

Notice that the circuit in Fig. 3.4.3 is similar to the wired AND circuit in Fig. 3.4.2, except that the two open collector AND gates have been replaced by two open collector NAND gates. The main difference with this circuit however is that to obtain an OR function from what appears to be a wired AND function, Negative Logic is applied.

Fig 3.4.4 Active Zero

Negative Logic

In Digital Electronics it is usual to explain the operation of a circuit theoretically in terms of 1 and 0, but the actual gates are really just specialised analogue circuits. As explained in Module 3.3, the outputs normally thought of as 1s and 0s are really ranges of voltage and current, 1 and 0 are no more than convenient names given to these voltages and currents. It is also usually assumed that logic 1 refers to the higher of the two voltage ranges − but that need not be so! Also logic 1 is normally the active state of an output, and logic 0 is the inactive state, but this is not always what is required.

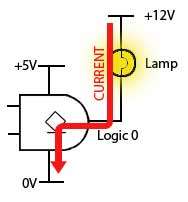

The source current available from an open collector gate output when it is at logic 1 is very small, compared to the current the gate will sink when its output transistor is turned on, giving an output of logic 0.

It is quite reasonable therefore, to drive some output device, such as a lamp or relay for example, using the higher current available from a logic 0 output, as shown in Fig. 3.4.4.

In negative logic it is assumed that the active state is the low voltage state and that this is called logic 1. What this does to the familiar truth tables used in positive logic is to replace all the logic 1s (previously assumed to be the active state) with logic 0s and vice versa.

The effect of this reversal of logic states can be seen in Table 3.4.1. The X column for the positive AND gate is as would be expected; a logic 1 when both A and B are 1, otherwise logic 0s. However using negative logic on the same physical AND gate, simply swapping the 1s and 0s in both the input and output columns has changed the X output column from three 0s and a 1, to three 1s and a 0, so that X = 1 whenever A or B is 1. The AND gate has been transformed to an OR gate!

Using negative logic will change the function of any of the six two input logic gates, if you want to see what happens, try re-writing the truth tables for AND, OR, NAND, NOR, XOR, and XNOR in a similar manner to Table 3.4.1. However, negative logic is not widely used and so unless a logic circuit is actually described as using negative logic, it can be assumed that positive logic is being applied.

Fig. 3.4.5 How the Wired OR Circuit Works

Negative Logic and the Wired OR Circuit

Fig. 3.4.5 shows how the wired AND circuit shown in Fig. 3.4.2 is made to work as the wired OR in Fig. 3.4.3. The only physical change is that the two AND gates have been replaced by two NAND gates; this has the effect of inverting the inputs of the ‘invisible’ wired AND gate. According to De Morgan’s Theorem, this has the effect of converting an AND gate into a NOR gate.

To implement negative logic however, and change the invisible AND gate to an OR gate, both the inputs and the outputs must be inverted, changing all the 1s to 0s and 0s to 1s. The inversion ‘bubble’ is shown at the output of the wired OR gate because the active state of the output is chosen to be the low voltage output normally called the logic 0 inactive state, but now using negative logic as shown in Fig. 3.4.5, the low voltage output is considered to be the ‘active logic 1’ state using negative logic.

If positive logic is used however, and logic the low voltage output from the invisible wired AND gate called the inactive logic 0 state, the output of the wired gate is logic of the circuit is that of a wired NOR gate.

Fig 3.4.6 Open Collector/Drain Buffer ICs

Buffers

Buffers in digital electronics are special gates inserted between one circuit and another to reduce any unwanted interaction between the two. The gates in buffer ICs typically have high impedance inputs and low impedance outputs, giving larger fan out factors than standard gates. Another common use is to enable a logic circuit having a low voltage and/or low current output to drive a circuit or output device requiring higher voltage or current than is available for standard logic ICs.

Open Collector Buffers

Typical ICs using buffered output gates are shown in Fig. 3.4.6. Buffered inverters and non-inverters are common, but there are also gates with other logic functions that have buffered outputs, including some open collector gates, such as the 74HC03 Quad 2 input NAND with open drain from NXP Semiconductors.

Open collector buffers such as the SN74LS06 Hex inverter buffer/driver IC, and the non-inverting buffer SN7407 from Texas Instruments, allow devices such as lamps, motors and relays for example, that normally require higher currents and voltages, to be driven directly from a low voltage logic circuit.

Schmitt Gates

Fig. 3.4.7 Schmitt Gates

The digital signals processed by logic gates need to have fast rising and falling edges. Taking too much time to change logic states, spending too long in the ‘invalid’ zone between states, can cause unreliable logic levels, timing problems and excessive power dissipation, even shortening the life of logic ICs. Standard gate inputs change from 0 to 1 or 1 to 0 at a voltage of about 2.0V. If there is any noise on the input signal, it may be rapidly changing its voltage above and below this level, so causing the gate to rapidly change state if the noise exceeds the noise margin. These rapid and uncertain changes in the gate’s input circuit will also cause the output to oscillate between 1 and 0, transmitting the problem to any subsequent gates in the digital system.

To avoid these problems, gates with Schmitt inputs such as those shown in Fig. 3.4.7 are often used, especially at the input to a system where noise may be expected, as signals arrive from an external source.

Schmitt gates use positive feedback, which causes the gate to switch between logic states extremely quickly. They also have a hysteresis effect, which only allows a change of state to occur as the input voltage passes two specific and different voltages, the Positive-going input threshold voltage (VT+) and the Negative-going input threshold voltage (VT-).

Fig. 3.4.8 Schmitt Gate Action

As the input voltage passes VT+ during a positive going transition, the gate input changes very rapidly to its high state. It then cannot return to its low state until the input voltage falls to the lower level of VT-.

This action has several beneficial effects on poor input signals, as illustrated in Fig. 3.4.8.

(a) It can be used to change slowly changing signals to square waves having very fast transitions.

(b) Noise can be removed from signals, provided that the amplitude of the noise is not greater than ΔVT.

(c) Slow rise and fall times can be restored to practically instant transitions by feeding the signal through a Schmitt trigger.

74 Series Schmitt Gates

Typical Schmitt Hex inverter and Quad NAND gate ICs from the 74 series are illustrated in Fig. 3.4.9.

Fig 3.4.9 Schmitt Input ICs

Sequential Logic

Introduction

The logic circuits discussed in Digital Electronics Module 4 had output states that depended on the particular combination of logic states at the input connections to the circuit. For this reason these circuits are called combinational logic circuits.

Use Module 5 to learn about digital circuits that use SEQUENTIAL LOGIC.

In these circuits the output depends, not only on the combination of logic states at its inputs, but also on the logic states that existed previously. In other words the output depends on a SEQUENCE of events occurring at the circuit inputs. Examples of such circuits include clocks, flip-flops, bi-stables, counters, memories, and registers. The actions of these circuits depend on a range of basic sub-circuits.

Clock Circuits

Module 5.1 deals with clock oscillators, which are basically types of square wave generators or oscillators that produce a continuous stream of square waves or a continuous train of pulses (a "square" wave whose mark to space ratio is NOT 1:1). These pulses are used to sequence the actions of other devices in the sequential logic circuit so that all the actions taking place in the circuit are properly synchronised.

Bi-Stable Logic Devices

Bi-stable devices (popularly called Flip-flops) described in Modules 5.2 to 5.4, are sub-circuits, usually contained within ICs, and are the most basic type of 1-bit memory. They have outputs that can take up one of two stable states, Logic 1 or logic 0 or off. Once the device is triggered into one of these two states by an external input pulse, the output remains in that state until another pulse is used to reverse that state, so that a logic 1 output becomes logic 0 or vice versa. Again the circuit remains stable in this state until an input signal is used to reverse the output state. Hence the circuit is said to have Bi (two) stable output states.

Counters

Various types of digital counters are described in Module 5.6. Consisting of arrangements of bi-stables, they are very widely used in many types of digital systems from computer arithmetic to TV screens, as well as many digital timing and measurement devices.

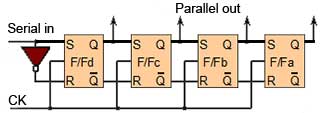

Registers

Also consisting of arrays of bi-stable elements, the shift registers described in Module 5.7 are temporary storage devices (memories) for multi-bit digital data. The data can be stored in the register either one bit at a time (serial input) or as one or more bytes at a time (parallel input).

The register can then output the data in either serial or parallel form. Shift registers are vital to receiving or transmitting data in digital communications systems. They can also be used in digital arithmetic for operations such as multiplication and division.

A Simple ALU

A simple arithmetic and logic unit (ALU) is described in Module 5.8 and combines many of the combinational and sequential logic circuits described in modules 4 and 5 to demonstrate how a very complex application is built by combining a number of much simpler digital sub circuits.

Clocks and Timing Signals

Most sequential logic circuits are driven by a clock oscillator. This usually consists of an astable circuit producing regular pulses that should ideally:

1. Be constant in frequency

Many clock oscillators use a crystal to control the frequency. Because crystal oscillators generate normally high frequencies, where lower frequencies are required the original oscillator frequency is divided down from a very high frequency to a lower one using counter circuits.

2. Have fast rising and falling edges to its pulses.

It is the edges of the pulses that are important in timing the operation of many sequential circuits, the rise and fall times are usually be less than 100ns. The outputs of clock circuits will typically have to drive more gates than any other output in a given system. To prevent this load distorting the clock signal, it is usual for clock oscillator outputs to be fed via a buffer amplifier.

3. Have the correct logic levels

The signals produced by the clock circuits must have appropriate the logic levels for the circuits being supplied.

Simple Clock Oscillator

Fig. 5.1.1 Simple Schmitt Inverter Clock Oscillator

Fig 5.1.1 is probably the simplest oscillator possible, having only three components. Notice that the gate is a Schmitt inverter. This device has an extremely fast change over between logic states. Also the level at which it responds to an input change from 0 to 1 (Vt+) is higher than the level at which it changes from 1 to 0 (Vt-). The operation of the circuit is as follows.

Suppose the gate input is at logic 0, because the gate is an inverter, the output must be at logic 1, and C will therefore charge up via R from the output. This will happen with the normal CR charging curve. Once Vt+ is reached at the gate input, the gate output will rapidly switch to 0. The resistor is now connected effectively between the positive plate of C and zero volts. Thus the capacitor now discharges via R until the gate input voltage reduces to Vt- when the output will change to logic 1 once more, starting the charging and discharging cycle over again.

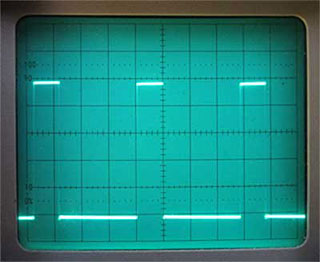

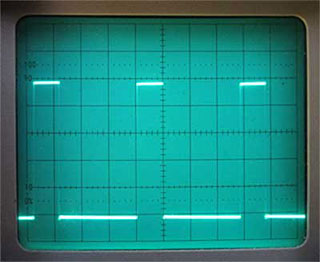

Fig. 5.1.2 Typical Basic Schmitt Oscillator Output

This Schmitt RC oscillator can produce a pulse waveform with an excellent wave shape and very fast rise and fall times. The mark to space ratio, as shown in Fig 5.1.2 is approximately 1:3.

The frequency of oscillation depends on the time constant of R and C, but is also affected by the characteristics of the logic family used. For the 74HC14 the frequency (ƒ)is calculated by:

When using the 74HCT14 the 0.8 correction factor is replaced by 0.67, however either of these formulae will give an approximate frequency. Whichever logic family is used, the frequency will vary with changes in supply voltage. Although this basic oscillator gives an excellent performance in many simple applications, if a stable frequency is an important factor in the choice of clock oscillator, there are of course better options.

Crystal Controlled Clock Oscillator

Fig. 5.1.3 Crystal Controlled Clock Oscillator

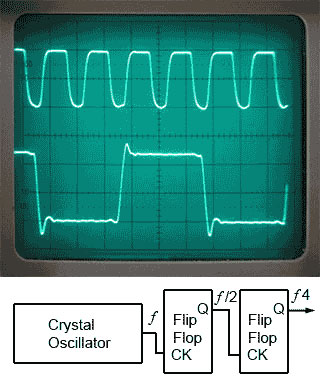

Fig. 5.1.3 uses three gates from a 74HCT04 IC, and a crystal to provide an accurate frequency of oscillation. Here, the oscillator is running at 3.276MHz but this can be reduced by dividing the output frequency down to a lower value by dividing it by 2 a number of times using a series of flip-flops.

The top waveform in Fig 5.1.4 shows the clock signal generated by Fig 5.1.3, and beneath it is the clock signal frequency divided by 4 after passing it through two flip-flops. Notice that after passing the signal through flip-flops, as well as being reduced in frequency, the wave shape is considerably squarer and now has a 1:1 mark to space ratio.

Fig. 5.1.4 Clock Frequency Divided by 4

The 555 Timer Clock Generator

Another option in circuits not requiring very high frequency clock signals is to use the 555 Timer in astable mode as a clock generator. This IC is able to produce good quality pulse or square wave signals over a wide range of frequencies, lower than those possible with crystal oscillators, also the frequency stability will not be as good as with crystal controlled oscillators. Several oscillator design options are discussed in Oscillators Module 4.4

Two Phase Clock Signals

Some older microprocessor systems required two-phase clock signals which, provided that the source clock signal operated at twice the frequency required by the microprocessor, saved processing time as the microprocessor was able to carry out two actions per clock cycle instead of one.

Producing a Two-Phase Clock Signal

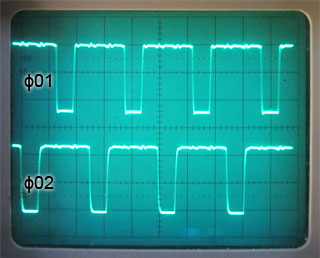

If a clock signal with a 1:1 mark space ratio is used, two non-overlapping clock pulses can be created, using the circuit shown in Fig 5.1.5. These signals are usually called Φ01 and Φ02 (Φ the Greek letter Phi is used to indicate phase).

Fig. 5.1.5 Two-Phase Clock Generator

In Fig 5.1.5 a single clock signal having a 1:1 mark to space ratio is fed into a JK flip-flop working in toggle mode. This is achieved by making both J and K logic 1. The active low PR and CLR inputs take no part in the operation of this circuit so are also tied to logic 1. In toggle mode the Q output of the JK flip-flop inverts the logic levels at Q and Q at every falling edge of the clock(CK) input, also Q and Q output always remaing at opposite logic states.

Each of the NAND gates will then produce a logic 0 output whenever both its inputs are at logic 1. The NAND gate producing Φ01 therefore creates a logic 0 pulse whenever CK and Q are at logic 1, and the NAND gate producing Φ02 creates a logic 0 pulse whenever CK and Q are at logic 1.

Fig. 5.1.6 Two-Phase Clock Signal

Fig. 5.1.6 illustrates the operation of Fig 5.1.5. Each of the NAND gates will produce a logic 0 output whenever both its inputs are at logic 1. The NAND gate producing Φ01 therefore creates a logic 0 pulse whenever CK and Q are at logic 1, and the NAND gate producing Φ02 creates a logic 0 pulse whenever CK and Q are at logic 1. Typical output waveforms are illustrated in Fig. 5.1.7.

If positive going clock pulses are required, the outputs from the NAND gates may be inverted using Schmitt inverters, which will also help to sharpen the rise and fall times of the clock waveforms.

Distributing Clock Signals

For more demanding applications there are very many specialised clock oscillator ICs available that are typically optimised for a particular range of applications, such as computer hardware, wireless communications, automotive or medical applications etc.

Clock Fan-out

Whatever circuit is used to generate a clock signal, it is important that its output has sufficient fan-out capability to drive the necessary number of ICs requiring a clock input, and that the clock signal is not degraded in amplitude, speed of its rise and fall times or accuracy of its frequency. Also, by maintaining fast rise and fall times, ringing on the waveform can become a problem. The waveform should be kept as close as possible to a perfect square wave shape.

Fig. 5.1.7 Two Phase Clock Waveforms

Circuit Capacitance

Because the clock must feed many gates, the small capacitance of each of these gates will add, to become an appreciable capacitance, which loads the clock output tending to slow the rise and fall time of the clock signal. To avoid this, the clock output must have a low enough impedance to rapidly charge and discharge any natural capacitance in the circuit. The usual way to achieve this is to feed the clock signal via a special clock buffer gate, which will have the necessary low output impedance and a large fan out factor. Schmitt trigger gates may also be used to restore the shape and integrity of clock signals before they are applied to gates in different parts of the circuit.

Cross-talk

Where the clock signal has to be distributed around large circuits, there is a greater chance of introducing noise, and possible ‘cross-talk’ where data in one conductor is radiated into another nearby conductor. Problems such as this will increase the likelihood of ‘skew’ errors, i.e. clock signals arriving at different parts of the circuit at slightly different times, due to small changes in the phase of some of the distributed clock signals. Miniaturisation brought about by surface mount technology can help minimise these problems. Also when clock signals need to be sent from one system to another over an external wired or wireless link it is common to use one of the several ECL or LVDS logic families with their differential outputs to minimise interference, and there are many application specific ICs (ASICS) using these technologies for high frequency clock distribution.

Digital Counters

Fig. 5.6.1 Four-bit Asynchronous Up Counter

Fig. 5.6.2 Four-bit Asynchronous Up Counter Waveforms

Asynchronous Counters.

Counters, consisting of a number of flip-flops, count a stream of pulses applied to the counter’s CK input. The output is a binary value whose value is equal to the number of pulses received at the CK input.

Each output represents one bit of the output word, which, in 74 series counter ICs is usually 4 bits long, and the size of the output word depends on the number of flip-flops that make up the counter. The output lines of a 4-bit counter represent the values 20, 21, 22 and 23, or 1,2,4 and 8 respectively. They are normally shown in schematic diagrams in reverse order, with the least significant bit at the left, this is to enable the schematic diagram to show the circuit following the convention that signals flow from left to right, therefore in this case the CK input is at the left.

Four Bit Asynchronous Up Counter

Fig. 5.6.1 shows a 4 bit asynchronous up counter built from four positive edge triggered D type flip-flops connected in toggle mode. Clock pulses are fed into the CK input of FF0 whose output, Q0 provides the 20 output for FF1 after one CK pulse.

The rising edge of the Q output of each flip-flop triggers the CK input of the next flip-flop at half the frequency of the CK pulses applied to its input.

The Q outputs then represent a four-bit binary count with Q0 to Q3 representing 20 (1) to 23 (8) respectively.

Assuming that the four Q outputs are initially at 0000, the rising edge of the first CK pulse applied will cause the output Q0 to go to logic 1, and the next CK pulse will make Q0 output return to logic 0, and at the same time Q0 will go from 0 to 1.

As Q0 (and the CK input of FF1 goes high) this will now make Q1 high, indicating a value of 21 (210) on the Q outputs.

The next (third) CK pulse will cause Q0 to go to logic 1 again, so both Q0 and Q1 will now be high, making the 4-bit output 11002 (310 remembering that Q0 is the least significant bit).

The fourth CK pulse will make both Q0 and Q1 return to 0 and as Q1 will go high at this time, this will toggle FF2, making Q2 high and indicating 00102 (410) at the outputs.

Reading the output word from right to left, the Q outputs therefore continue to represent a binary number equalling the number of input pulses received at the CK input of FF0. As this is a four-stage counter the flip-flops will continue to toggle in sequence and the four Q outputs will output a sequence of binary values from 00002 to 11112 (0 to 1510) before the output returns to 00002 and begins to count up again as illustrated by the waveforms in Fig 5.6.2.

Fig. 5.6.3 Four-bit Asynchronous Down Counter

Four Bit Asynchronous Down Counter

To convert the up counter in Fig. 5.6.1 to count DOWN instead, is simply a matter of modifying the connections between the flip-flops. By taking both the output lines and the CK pulse for the next flip-flop in sequence from the Q output as shown in Fig. 5.6.3, a positive edge triggered counter will count down from 11112 to 00002.

Although both up and down counters can be built, using the asynchronous method for propagating the clock, they are not widely used as counters as they become unreliable at high clock speeds, or when a large number of flip-flops are connected together to give larger counts, due to the clock ripple effect.

Fig.5.6.4 Timing Diagram Detail Showing Clock Ripple

Clock Ripple

The effect of clock ripple in asynchronous counters is illustrated in Fig. 5.6.4, which is a magnified section (pulse 8) of Fig. 5.6.2.

Fig. 5.6.4 shows how the propagation delays created by the gates in each flip-flop (indicated by the blue vertical lines) add, over a number of flip-flops, to form a significant amount of delay between the time at which the output changes at the first flip flop (the least significant bit), and the last flip flop (the most significant bit).

As the Q0 to Q3 outputs each change at different times, a number of different output states occur as any particular clock pulse causes a new value to appear at the outputs.

At CK pulse 8 for example, the outputs Q0 to Q3 should change from 11102 (710) to 00012 (810), however what really happens (reading the vertical columns of 1s and 0s in Fig. 5.6.4) is that the outputs change, over a period of around 400 to 700ns, in the following sequence:

- 11102 = 710

- 01102 = 610

- 00102 = 410

- 00002 = 010

- 00012 = 810

At CK pulses other that pulse 8 of course, different sequences will occur, therefore there will be periods, as a change of value ripples through the chain of flip-flops, when unexpected values appear at the Q outputs for a very short time. However this can cause problems when a particular binary value is to be selected, as in the case of a decade counter, which must count from 00002 to 10012 (910) and then reset to 00002 on a count of 10102 (1010).

These short-lived logic values will also cause a series of very short spikes on the Q outputs, as the propagation delay of a single flip-flop is only about 100 to 150ns. These spikes are called ‘runt spikes’ and although they may not all reach to full logic 1 value every time, as well as possibly causing false counter triggering, they must also be considered as a possible cause of interference to other parts of the circuit.

Although this problem prevents the circuit being used as a reliable counter, it is still valuable as a simple and effective frequency divider, where a high frequency oscillator provides the input and each flip-flop in the chain divides the frequency by two.

Synchronous Counters

The synchronous counter provides a more reliable circuit for counting purposes, and for high-speed operation, as the clock pulses in this circuit are fed to every flip-flop in the chain at exactly the same time. Synchronous counters use JK flip-flops, as the programmable J and K inputs allow the toggling of individual flip-flops to be enabled or disabled at various stages of the count. Synchronous counters therefore eliminate the clock ripple problem, as the operation of the circuit is synchronised to the CK pulses, rather than flip-flop outputs.

Synchronous Up Counter

Fig.5.6.5 Synchronous Clock Connection

Fig. 5.6.5 shows how the clock pulses are applied in a synchronous counter. Notice that the CK input is applied to all the flip-flops in parallel. Therefore, as all the flip-flops receive a clock pulse at the same instant, some method must be used to prevent all the flip-flops changing state at the same time. This of course would result in the counter outputs simply toggling from all ones to all zeros, and back again with each clock pulse.

However, with JK flip-flops, when both J and K inputs are logic 1 the output toggles on each CK pulse, but when J and K are both at logic 0 no change takes place.

Fig. 5.6.6 The First Two Stages of a Synchronous Counter

Fig. 5.6.6 shows two stages of a synchronous counter. The binary output is taken from the Q outputs of the flip-flops. Note that on FF0 the J and K inputs are permanently wired to logic 1, so Q0 will change state (toggle) on each clock pulse. This provides the ‘ones’ count for the least significant bit.

On FF1 the J1 and K1 inputs are both connected to Q0so that FF1 output will only be in toggle mode when Q0is also at logic 1. As this only happens on alternate clock pulses, Q1 will only toggle on even numbered clock pulses giving a ‘twos’ count on the Q1 output.

Table 5.6.1 shows this action, where it can be seen that Q1 toggles on the clock pulse only when J1 and K1 are high, giving a two bit binary count on the Q outputs, (where Q0 is the least significant bit).

In adding a third flip flop to the counter however, direct connection from J and K to the previous Q1 output would not give the correct count. Because Q1 is high at a count of 210 this would mean that FF2 would toggle on clock pulse three, as J2 and K2 would be high. Therefore clock pulse 3 would give a binary count of 1112 or 710 instead of 410.

Fig. 5.6.7 Adding a Third Stage

To prevent this problem an AND gate is used, as shown in Fig. 5.6.7 to ensure that J2 and K2 are high only when both Q0and Q1 are at logic 1 (i.e. at a count of three). Only when the outputs are in this state will the next clock pulse toggle Q2 to logic 1. The outputs Q0 and Q1 will of course return to logic 0 on this pulse, so giving a count of 0012 or 410 (with Q0 being the least significant bit).

Fig. 5.6.8 shows the additional gating for a four stage synchronous counter. Here FF3 is put into toggle mode by making J3 and K3 logic 1, only when Q0 Q1 and Q2 are all at logic 1.

Q3 therefore will not toggle to its high state until the eighth clock pulse, and will remain high until the sixteenth clock pulse. After this pulse, all the Q outputs will return to zero.

Note that for this basic form of the synchronous counter to work, the PR and CLR inputs must also be all at logic 1, (their inactive state) as shown in Fig. 5.6.8.

Synchronous Down Counter

Converting the synchronous up counter to count down is simply a matter of reversing the count. If all of the ones and zeros in the 0 to 1510 sequence shown in Table 5.6.2 are complemented, (shown with a pink background) the sequence becomes 1510 to 0.

Down Counter Circuit

As every Q output on the JK flip-flops has its complement on Q, all that is needed to convert the up counter in Fig. 5.6.8 to the down counter shown in Fig 5.6.9 is to take the JK inputs for FF1 from the Q output of FF0 instead of the Q output. Gate TC2 now takes its inputs from the Q outputs of FF0 and FF1, and TC3 also takes its input from FF2 Q output.

Up/Down Counter

Fig. 5.6.10 illustrates how a single input, called (UP/DOWN) can be used to make a single counter count either up or down, depending on the logic state at the UP/DOWN input.

Each group of gates between successive flip-flops is in fact a modified data select circuit described in Combinational Logic Module 4.2, but in this version an AND/OR combination is used in preference to its DeMorgan equivalent NAND gate circuit. This is necessary to provide the correct logic state for the next data selector.

The Q and Q outputs of flip-flops FF0, FF1 and FF2 are connected to what are, in effect, the A and B data inputs of the data selectors. If the control input is at logic 1 then the CK pulse to the next flip-flop is fed from the Q output, making the counter an UP counter, but if the control input is 0 then CK pulses are fed from Q and the counter is a DOWN counter.

Synchronous BCD Up Counter

A typical use of the CLR inputs is illustrated in the BCD Up Counter in Fig 5.6.11. The counter outputs Q1 and Q3 are connected to the inputs of a NAND gate, the output of which is taken to the CLR inputs of all four flip-flops. When Q1 and Q3are both at logic 1, the output terminal of the limit detection NAND gate (LD1) will become logic 0 and reset all the flip-flop outputs to logic 0.

Because the first time Q1 and Q3 are both at logic 1 during a 0 to 1510 count is at a count of ten (10102), this will cause the counter to count from 0 to 910 and then reset to 0, omitting 1010 to 1510.

The circuit is therefore a BCD8421 counter, an extremely useful device for driving numeric displays via a BCD to 7-segment decoder etc. However by re-designing the gating system to produce logic 0 at the CLR inputs for a different maximum value, any count other than 0 to 15 can be achieved.

If you already have a simulator such as Logisim installed on your computer, why not try designing an Octal up counter for example.

Fig. 5.6.12 Counter IC Inputs and Outputs

Counter IC Inputs and Outputs

Although synchronous counters can be, and are built from individual JK flip-flops, in many circuits they will be ether built into dedicated counter ICs, or into other large scale integrated circuits (LSICs).

For many applications the counters contained within ICs have extra inputs and outputs added to increase the counters versatility. The differences between many commercial counter ICs are basically the different input and output facilities offered. Some of which are described below. Notice that many of these inputs are active low; this derives from the fact that in earlier TTL devices any unconnected input would float up to logic 1 and hence become inactive. However leaving inputs un-connected is not good practice, especially CMOS inputs, which float between logic states, and could easily be activated to either valid logic state by random noise in the circuit, therefore ANY unused input should be permanently connected to its inactive logic state.

Enable Inputs

ENABLE (EN) inputs on counter ICs may have a number of different names, e.g. Chip Enable (CE), Count Enable (CTEN), Output Enable (ON) etc., each denoting the same or similar functions.

Count Enable (CTEN) for example, is a feature on counter integrated circuits, and in the synchronous counter illustrated in Fig 5.6.13, is an active low input. When it is set to logic 1, it will prevent the count from progressing, even in the presence of clock pulses, but the count will continue normally when CTEN is at logic 0.

A common way of disabling the counter, whilst retaining any current data on the Q outputs, is to inhibit the toggle action of the JK flip-flops whilst CTEN is inactive (logic 1), by making the JK inputs of all the flip-flops logic 0. However, as the logic states of the JK inputs of FF1, FF2 and FF3 depend on the state of the previous Q output, either directly or via gates T2 and T3, in order to preserve the output data, the Q outputs must be isolated from the JK inputs whenever CTEN is logic 1, but the Q outputs must connect to the JK inputs when CTEN is at logic 0 (the count enabled state).

This is achieved by using the extra (AND) enable gates, E1, E2 and E3, each of which have one of their inputs connected to CTEN (the inverse of CTEN). When the count is disabled, CTEN and therefore one of the inputs on each of , E1, E2 and E3 will be at logic 0, which will cause these enable gate outputs, and the flip-flop JK inputs to also be at logic 0, whatever logic states are present on the Q outputs, and also at the other enable gate inputs. Therefore whenever CTEN is at logic 1 the count is disabled.

When CTEN is at logic 0 however, CTEN will be logic 1 and E1, E2 and E3 will be enabled, causing whatever logic state is present on the Q outputs to be passed to the JK inputs. In this condition, when the next clock pulse is received at the CK input the flip-flops will toggle, following their normal sequence.

Asynchronous Parallel Load